NEC V20

8 MHz V20 in plastic DIP package | |

| General information | |

|---|---|

| Launched | March 1984[1] |

| Common manufacturers | |

| Performance | |

| Data width | 16 bits |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Co-processor |

|

| History | |

| Successor | NEC V60 |

The NEC V20 is a microprocessor that was designed and produced by NEC. It is both pin compatible and object-code compatible with the Intel 8088, with an instruction set architecture (ISA) similar to that of the Intel 80188 with some extensions.[2] The V20 was introduced in March 1984.[1][2]

Features

[edit]The V20's die comprised 63,000 transistors; more than double the 29,000 of the 8088 CPU.[1] The chip was designed for a clock duty cycle of 50%, compared to the 33% duty cycle used by the 8088.[3] The V20 has two 16-bit wide internal databuses, allowing two data transfers to occur concurrently.[4] Differences like that meant that a V20 could typically complete more instructions in a given time than an Intel 8088 running at the same frequency.[2]

The V20 was fabricated in 2-micron CMOS technology.[5][3] Early versions ran at speeds of 5, 8, and 10 MHz.[6]: 2 In 1990, an upgrade to the fabrication process technology resulted in the V20H and V20HL, with improved performance and reduced power consumption.[5] Later versions added speeds of 12 and 16 MHz. The V20HLs were also completely static, allowing their clock to be stopped.

The V20 was described as 16-bits wide internally. It used an 8-bit external data bus that was multiplexed onto the same pins as the low byte of the address bus. Its 20-bit wide address bus was able to address 1 MB of memory.

The V20 was reported to have been compatible with the Intel 8087 floating-point unit (FPU) coprocessor.[7] NEC also designed their own FPU, the μPD72091, which was cancelled before reaching production. They followed this with a revised design, the μPD72191, but it is unclear how many, if any, of this second part were produced.[8]

The V30, a nearly identical CPU with a 16-bit wide external data bus, debuted on March 1, 1984.[9][5] It was pin and object-code compatible with the Intel 8086.

ISA extensions

[edit]

The V20's ISA includes several instructions not executed by the 8088, with instructions for bit manipulation, packed BCD operations, multiplication, and division. They also include new real-mode instructions from the Intel 80286.[10]

The ADD4S, SUB4S, and CMP4S instructions were able to add, subtract, and compare huge packed binary-coded decimal numbers stored in memory. Instructions ROL4 and ROR4 rotate four-bit nibbles. Another family consisted of the TEST1, SET1, CLR1, and NOT1 instructions, which test, set, clear, and invert single bits of their operands, but are far less efficient than the later i80386 equivalents BT, BTS, BTR, and BTC; neither are their encodings compatible. There were two instructions to extract and insert bit fields of arbitrary lengths (EXT, INS). And finally, there were two additional repeat prefixes, REPC and REPNC, which amended the original REPE and REPNE instructions for scanning a string of bytes or words (with instructions SCAS and CMPS) while a less or not less condition remained true.[11]

The V20 offered a mode that emulated an Intel 8080 CPU. A BRKEM instruction is issued to start 8080 emulation. The operand of the instruction specifies an interrupt number whose vector contains the segment:offset where emulation is to begin. To end, a RETEM instruction is issued in 8080 code. One feature not often employed is the CALLN (call native) which issues an 8086-type interrupt call that enables x86 code (which returns using an IRET) to be mixed in with 8080 code.

Another mode put the processor into a power-saving state via a HALT instruction.[6][7]

Lawsuits

[edit]In 1982, Intel sued NEC over the latter's μPD8086 and μPD8088. This suit was settled out of court, with NEC agreeing to license the designs from Intel.[12]

In late 1984, Intel again filed suit against NEC, claiming that the microcode in the V20 and V30 infringed its patents for the 8088 and 8086 processors.[13] NEC software engineer Hiroaki Kaneko had studied both the hardware design of the Intel CPUs and the original Intel microcode.

In its ruling, the court determined that the microcode in the control store constitutes a computer program, and so is protected by copyright.[14] They further found Intel to have forfeited their copyright by neglecting to ensure that all second-source chips were suitably marked. The court also determined that NEC did not simply copy Intel's microcode, and that the microcode in the V20 and V30 was sufficiently different from Intel's to not infringe Intel's patents.

The judge in the case accepted NEC's cleanroom evidence. He also approved of NEC's use of reverse engineering with respect to the creation of NEC's Rev.2 microcode, without commenting on it with respect to the Rev.0 code.[14]: 212–221

Variants and successors

[edit]

| Product | Part no. | Details |

|---|---|---|

| NEC V30 | μPD70116 | Essentially an NEC V20 with a 16-bit external data bus, the V30 was pin compatible with the Intel 8086. The V30 was a factory upgrade from the 8086 used in the GTD-5 EAX Class 5 central office switch. It was also used in the Psion Series 3, the NEC PC-9801VM, the Olivetti PCS86, the Applied Engineering "PC Transporter" card for the Apple II series of computers, and in various arcade machines (particularly ones made by Irem) in the late 1980s. Years later, a low-voltage V30 MZ version was used in Bandai's handheld WonderSwan game console. |

| NEC V20HL | μPD70108H | High-speed (up to 16 MHz), low-power version of the V20. |

| NEC V30HL | μPD70116H | High-speed (up to 16 MHz), low-power version of the V30. |

| NEC V25 | μPD70320 | A microcontroller version of the NEC V20. |

| NEC V25HS | μPD79011 | A version of the V25 with the RX116 RTOS in the internal ROM. |

| NEC V25+ | μPD70325 | High-speed version of the V25. |

| NEC V33 | μPD70136 | A version of the V30 with separate address and data buses and with instruction decode done by hardwired logic rather than a microprogrammed control store. Throughput is twice as high as a V30 for the same clock frequency. The V33 has performance equivalent to Intel 80286. Memory address space is increased to 16M bytes. Two additional instructions, BRKXA and RETXA, support the extended addressing mode. 8080 emulation is not supported.

|

| NEC V33A | μPD70136A | Differs from the V33 in that it has interrupt vector numbers compatible with Intel's 80X86 processors. |

| NEC V35 | μPD70330 | A microcontroller version of the NEC V30. |

| NEC V35HS | μPD79021 | A version of the V35 with the RX116 RTOS in the internal ROM. |

| NEC V35+ | μPD70335 | A high-speed version of the V35. |

| NEC V40 | μPD70208 | An embedded version of the V20, integrated Intel-compatible 8251 USART, 8253 programmable interval timer, and 8255 parallel port interface. Used in the Olivetti PC1, Digisystems Jetta XD, the Sharp PC-4500 and the Zenith Eazy PC. |

| NEC V40HL | μPD70208H | A high-speed, low-voltage version of the V40. |

| NEC V50 | μPD70216 | An embedded version of the V30. It is the main CPU in the Akai S1000 and S1100, and the Korg M1.[15][16] |

| NEC V50HL | μPD70216H | A high-speed, low-voltage version of the V50. |

| NEC V41 | μPD70270 | Integrates a V30HL core and PC-XT peripherals: 8255 parallel port interface, 8254 programmable interval timer, 8259 PIC, 8237 DMA controller and 8042 keyboard controller. Also integrates full DRAM controller. |

| NEC V51 | μPD70280 | Integrates a V30HL core and PC-XT peripherals: 8255 parallel port interface, 8254 programmable interval timer, 8259 PIC, 8237 DMA controller and 8042 keyboard controller. Also integrates full DRAM controller. Was used in the Olivetti Quaderno PT-XT-20. |

| NEC V53 | μPD70236 | Integrates a V33 core with 4-channel DMA (μPD71071[17]/i8237), UART (μPD71051/i8251), three timer/counters (μPD71054/i8254) and interrupt controller (μPD71059/i8259). It was used in the Akai MPC3000[18][19] and Akai SG01v. |

| NEC V53A | μPD70236A | Integrates some peripherals with a V33A core. Used in Sharp Zaurus PI-B304/B308 |

| NEC V55PI | μPD70433 | The V55PI has extended segment registers called DS2 and DS3, and by shifting the register value by 8 bits to the left and adding an offset value, it is possible to access the entire 16MB address space.[20] |

| NEC V55SC | μPD70423 | The V55SC not only comes with extended segment registers, called DS2 and DS3, but is also furnished with a two-channel Multi Protocol Serial Controller (MPSC) which is subset of μPD72001/72002.[21] |

| Vadem VG230 | A single-chip PC platform.[22] The VG230 contained a 16 MHz NEC V30HL processor and IBM PC/XT-compatible core logic, LCD controller (CGA/AT&T640x400) with touch-plane support, keyboard matrix scanner, dual PCMCIA 2.1 card controller, EMS 4.0 hardware support for up to 64 MB, and built-in timer, PIC, DMA, UART and RTC controllers. It was used in the HP OmniGo 100, 120 and IBM Simon.[23] | |

| Vadem VG330 | Successor to the VG230, it contained a 32 MHz NEC V30MX processor and IBM PC/AT-compatible core logic with dual PICs, LCD controller (640x480), keyboard matrix scanner, PC Card ExCA 2.1 controller and SIR port. | |

| NEC V60 | μPD70616 | With the V60 processor, NEC departed from the x86 design and launched a new, 32-bit CISC architecture. The V60 and the V70, which differed mainly in the widths of their respective external address and data busses, both included a V20/V30 emulation mode.[24]: §10 [8] |

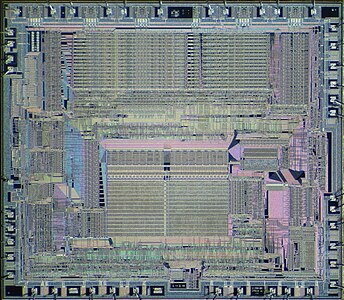

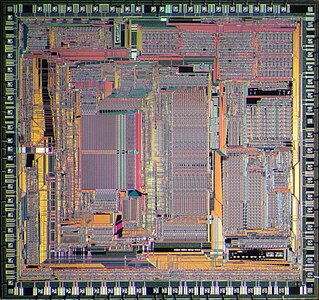

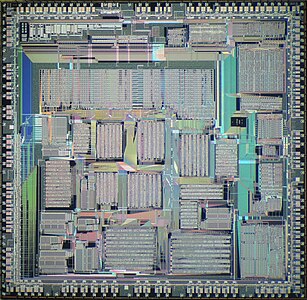

- Die photos

-

NEC V30

-

NEC V50

-

NEC V53

See also

[edit]- NEC RX116, dedicated ITRON-1-based 16-bit RTOS

- NEC μPD9002, a Z80 and x86 compatible CPU

- VIA Technologies Alternate Instruction Set, a CPU implementing a similar scheme to enter and exit into an alternate instruction set mode

References

[edit]- ^ a b c "8088 & V20". X86 CPU's Guide. 2018-11-17.

- ^ a b c Gennadiy, Shvets. "NEC V20 processor family". CPU-World.

- ^ a b Davis, Stephen R. (1985-12-24). "Turbocharging Your PC with the V-Series". PC Magazine. pp. 181–186.

- ^ Chodorek, Robert Ryszard (November–December 2021). "NEC V20: Inspiring, Inconspicuous". IEEE Micro. 41 (6): 158–159. doi:10.1109/MM.2021.3115870.

- ^ a b c 1983年 — 16bitマイクロプサッサV30の開発(NEC) [1983 — Development of the V30 16-bit Microprocessor (NEC)] (in Japanese). 2010-10-23. Archived from the original on 2019-07-13. Retrieved 2020-07-14.

- ^ a b μPD70108 — V20 16-/8-bit Microprocessor (PDF). NEC. June 1994.

- ^ a b Mahoney, Bob (1985-10-16). "Output of file: NECV20B.ALL contained in archive: NEC-V20.ZIP". The Programmer's Corner.

- ^ a b Culver, John (2021-09-01). "NEC's Forgotten FPUs". The CPU Shack.

- ^ "Nec V30 D70116C-10". X86 CPUS' GUIDE. 2020-07-15.

- ^ Hummel, Robert L. (1988-06-14). "PC Tutor — Mixing Processors". PC Magazine. pp. 377–378.

- ^ "NEC User's Manual, 16-Bit V Series, 16-/8- and 16-bit microprocessors, Instruction" (PDF). September 2000. Retrieved 2014-11-25.

- ^ Lemos, Robert (1998-06-08). "NEC case opened up market for cloning". ZDNet.

- ^ Parker, Rachel (1989-02-13). "Judge Declares Microcode Copyrightable". InfoWorld. p. 8.

- ^ a b Contreras, Jorge; Handley, Laura; Yang, Terrence (March–May 1990). "NEC v. Intel: Breaking New Ground in the Law of Copyright" (PDF). Harvard Journal of Law and Technology. 3: 209–222.

- ^ Korg M1 Service Manual

- ^ Russ, Martin (July 1989). "Korg M1R". Sound On Sound. United Kingdom. pp. 48–52. Retrieved 2022-08-13.

- ^ "pPD70236 (V53) 16-Bit Microprocessor: High-Speed, High-Integration, CMOS" (PDF). p. 316(3f1). Retrieved 2024-01-05.

- ^ "Mame/Mpc3000.CPP at 251b11266dcd394741e6b48c00a5c9131ef68673 · mamedev/Mame". GitHub. 2022-11-23.

- ^ "AKAI MPC 3000: The Best Drum Machine of All Time". Audio Jive. 2020-12-09.

- ^ "V55PI 16-BIT MICROPROCESSOR". pp. 21–22. Retrieved 2024-01-18.

- ^ "NEC V55SC 16-bit Microprocessor Preliminary Data Sheet (O.D.No ID-8206A, March 1993)" (PDF). pp. 1, 22. Retrieved 2024-01-21.

- ^ Vadem VG230 Developer's Manual

- ^ Nochkin, Alexander (2013-07-10). "IBM Simon — первый в мире смартфон. Что внутри?" [The IBM Simon is the world's first smartphone. What is inside?]. habr.com (in Russian).

- ^ μPD70616 Programmer's Reference Manual (PRELIMINARY ed.). NEC. November 1986.

Further reading

[edit]- V20/V30 User's Manual (PDF). NEC. October 1986. Archived from the original (PDF) on 2013-01-08. Alt URL

- Davis, Randy (December 1985 – January 1986). Written at Greenville, Texas, USA. "The New NEC Microprocessors - 8080, 8086, Or 8088?" (PDF). Micro Cornucopia. No. 27. Bend, Oregon, USA. pp. 4–7. ISSN 0747-587X. Archived (PDF) from the original on 2020-02-11. Retrieved 2020-02-11.

External links

[edit]- Buchty, Rainer. "Casiorama". www.buchty.net.

- "NEC V20". cpu-collection.de.

- Hinckley, Robert C. (January 1987). "NEC v. Intel: Will Hardware Be Drawn into the Black Hole of Copyright Editors'". Santa Clara High Technology Law Journal. Vol. 3, no. 1. pp. 23–72.