High Bandwidth Memory

La High Bandwidth Memory (HBM, en français : mémoire à large bande passante) est une interface de mémoire d’ordinateur pour la mémoire vive dynamique synchrone (SDRAM) empilée en 3D (en), initialement de Samsung, AMD et SK Hynix. Elle est utilisée en conjonction avec des accélérateurs graphiques hautes performances, des périphériques réseau, des ASIC de centres de données IA hautes performances, comme cache dans le boîtier de CPU[1] et comme RAM dans le boîtier de processeurs et FPGA à venir, et dans certains supercalculateurs (tels que le NEC SX-Aurora TSUBASA et le Fujitsu A64FX (en))[2]. La première puce mémoire HBM a été produite par SK Hynix en 2013[3] et les premiers appareils à utiliser la HBM étaient les GPU AMD Fiji en 2015[4],[5].

La mémoire à large bande passante a été adoptée par le JEDEC comme norme industrielle en octobre 2013[6]. La deuxième génération, HBM2, a été approuvée par le JEDEC en janvier 2016[7].

Technologie

[modifier | modifier le code]La HBM atteint une bande passante plus élevée que la DDR4 ou la GDDR5 tout en consommant moins d’énergie et dans un encombrement nettement plus faible[8]. Ceci est réalisé en empilant jusqu’à huit puces DRAM et une puce de base en option qui peut inclure un circuit tampon et une logique de test[9]. La pile est souvent connectée au contrôleur mémoire d’un GPU ou d’un CPU via un substrat, tel qu’un interposeur en silicium[10],[11]. Alternativement, la matrice de mémoire peut être empilée directement sur la puce CPU ou GPU. Dans la pile, les puces sont interconnectées verticalement par des vias traversant le silicium (TSV) et des microbosses (en). La technologie HBM est similaire dans son principe mais incompatible avec l’interface Hybrid Memory Cube (HMC) développée par Micron Technology[12].

Le bus mémoire HBM est très large par rapport aux autres mémoires DRAM telles que la DDR4 ou la GDDR5. Une pile HBM de quatre puces DRAM (4-Hi) a deux canaux 128 bits par puce, soit un total de 8 canaux et une largeur de bus totale de 1024 bits. Une carte graphique/GPU avec quatre piles 4-Hi HBM aurait donc un bus mémoire d’une largeur de 4096 bits. En comparaison, la largeur de bus des mémoires GDDR est de 32 bits, une carte graphique avec 16 canaux aura une interface mémoire de 512 bits[13]. HBM prend en charge jusqu’à 4 Go par boîtier.

Le plus grand nombre de connexions à la mémoire, par rapport à la DDR4 ou GDDR5, nécessitait une nouvelle méthode de connexion de la mémoire HBM au GPU (ou à un autre processeur)[14]. AMD et Nvidia ont tous deux utilisé des puces de silicium spécialement conçues, appelées interposeurs (en), pour connecter la mémoire et le GPU. Cet interposeur a l’avantage supplémentaire de nécessiter que la mémoire et le processeur soient physiquement proches, ce qui réduit les chemins de mémoire. Cependant, comme la fabrication de dispositifs semi-conducteurs est nettement plus chère que la fabrication de circuits imprimés, cela ajoute un coût au produit final.

Interface

[modifier | modifier le code]La DRAM HBM est étroitement couplée à la puce de calcul hôte avec une interface distribuée. L’interface est divisée en canaux indépendants. Les canaux sont complètement indépendants les uns des autres et ne sont pas nécessairement synchrones entre eux. La DRAM HBM utilise une architecture à interface large pour obtenir un fonctionnement à grande vitesse et à faible consommation. La DRAM HBM utilise une horloge différentielle à 500 MHz CK_t / CK_c (où le suffixe « _t » désigne la composante « vraie » ou « positive » de la paire différentielle, et « _c » signifie la composante « complémentaire »). Les commandes sont enregistrées sur le front montant de CK_t, CK_c. Chaque interface de canal possède un bus de données 128 bits fonctionnant à débit de données double (DDR). HBM prend en charge des taux de transfert de 1 GT/s par broche (transfert de 1 bit), ce qui donne une bande passante globale de 128 Go/s.

HBM2

[modifier | modifier le code]La deuxième génération de mémoire à large bande passante, HBM2, spécifie également jusqu’à huit puces par pile et double les taux de transfert, jusqu’à 2 GT/s par broche. En conservant un accès large de 1024 bits, HBM2 est capable d’atteindre 256 Go/s de bande passante mémoire par boîtier. La spécification HBM2 autorise jusqu’à 8 Go par boîtier. HBM2 devrait être particulièrement utile pour les applications grand public sensibles aux performances telles que la réalité virtuelle[15].

Le 19 janvier 2016, Samsung a annoncé un début de production de masse de HBM2, jusqu’à 8 Go par pile[16],[17]. SK Hynix a également annoncé la disponibilité de piles de 4 Go en août 2016[18].

-

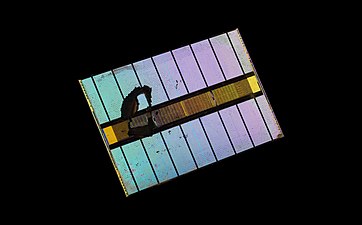

Puce DRAM HBM2

-

Puce contrôleur HBM2

-

L'interposeur HBM2 d'un GPU Radeon RX Vega 64, avec les puces HBM retirées ; le GPU est encore en place

Références

[modifier | modifier le code]- (en-US) Anton Shilov, « Intel Confirms On-Package HBM Memory Support for Sapphire Rapids », sur Tom's Hardware, (consulté le )

- (en) « ISSCC 2014 Trends (archivé depuis l'original) » [PDF], , page 118 "High-Bandwidth DRAM"

- (en) « These are the records of SK hynix’s growth since 1983 until today », sur SK Hynix (consulté le )

- (en-US) Ryan Smith, « The AMD Radeon R9 Fury X Review », Anandtech, (consulté le )

- (en-US) Timothy Prickett Morgan, « Future Nvidia 'Pascal' GPUs Pack 3D Memory, Homegrown Interconnect », EnterpriseTech, (consulté le ) : « Nvidia will be adopting the High Bandwidth Memory (HBM) variant of stacked DRAM that was developed by AMD and Hynix »

- (en) « High Bandwidth Memory (HBM) DRAM (JESD235)] », JEDEC,

- (en) « JESD235a: High Bandwidth Memory 2 », JEDEC,

- (en) Joonyoung Kim and Younsu Kim, « HBM: Memory Solution for Bandwidth-Hungry Processors (archivé depuis l'original) », SK& Hynix // Hot Chips,

- (en) Sohn et.al. (Samsung), « A 1.2 V 20 nm 307 GB/s HBM DRAM With At-Speed Wafer-Level IO Test Scheme and Adaptive Refresh Considering Temperature Distribution », IEEE Journal of Solid-State Circuits, vol. 52, no 1, , p. 250–260 (DOI 10.1109/JSSC.2016.2602221, Bibcode 2017IJSSC..52..250S, S2CID 207783774, lire en ligne)

- (en) « What's Next for High Bandwidth Memory », sur semiengineering.com,

- (en) « Interposers », sur semiengineering.com

- (en) « Where Are DRAM Interfaces Headed? (archivé depuis l'original) », EETimes, 4/18/2014, "The Hybrid Memory Cube (HMC) and a competing technology called High-Bandwidth Memory (HBM) are aimed at computing and networking applications. These approaches stack multiple DRAM chips atop a logic chip."

- (en) Mike O’Connor, Sr. Research Scientist, « Highlights of the HighBandwidth Memory (HBM) Standard », NVidia // The Memory Forum,

- (en-US) Ryan Smith, « AMD Dives Deep On High Bandwidth Memory – What Will HBM Bring to AMD? », Anandtech, (consulté le )

- (en) Theo Valich, « NVIDIA Unveils Pascal GPU: 16GB of memory, 1TB/s Bandwidth », sur VR World, (consulté le )

- (en) « Samsung Begins Mass Producing World's Fastest DRAM – Based on Newest High Bandwidth Memory (HBM) Interface », sur news.samsung.com

- (en) « Samsung announces mass production of next-generation HBM2 memory », ExtremeTech,

- (en) Anton Shilov, « SK Hynix Adds HBM2 to Catalog », Anandtech, (consulté le )